今回ご紹介するのは、学生による修士論文のための研究として実施した実例です。

目的は、高耐圧用ディスクリート素子のDouble Diffusion MOSFET(DMOS)のマクロモデル化です。同じ素子をVerilog-A言語を用いて、コンパクトモデルとして作成する部分は第3回に解説します。

簡易的なマクロモデル [1] によるモデル作成

回路シミュレーションを実践されている方は、電源回路や増幅器の出力段などにDMOSを使用している場合があるかと思います。このDMOSのモデルを通常の小信号MOSFET用モデルである、UCB MOSFETレベル2、3やBSIM3、4といった汎用モデルや、それらをシミュレータベンダーが改造したモデルなどを代用していることでしょう。その際、ドレイン抵抗関連のパラメータ値を変更して、できるだけDMOSの電気特性に近づけて使用します。

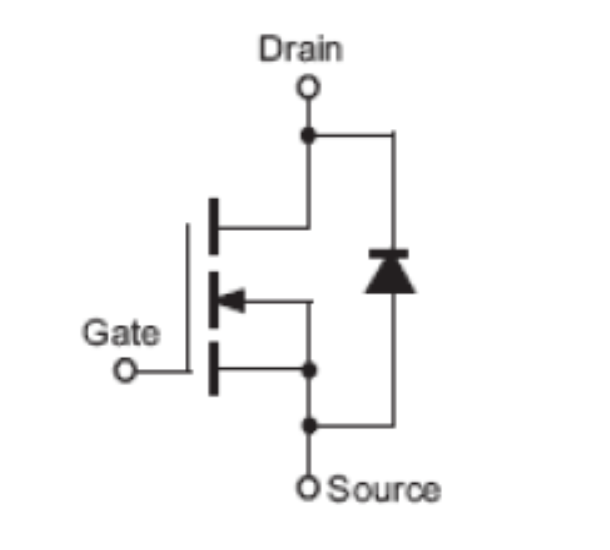

さらにモデルに詳しい方は、DMOSのデータシートなどに掲載されている等価回路を参照して、図1のようにソース・ドレイン間の保護ダイオードを付加して、2つのアクティブ素子によるマクロモデルを組んで使用すると思います。

図1 簡単なDMOSの等価回路例

マクロモデルの構成

マクロモデルのネットリストは、表1のようになります。なお、各ネットリストエレメントの意味については、SPICEシミュレータの解説書を参照してください。

表1 簡単なDMOSマクロモデルのネットリスト例

DIO 3 1 FWDIODE

MOS 1 2 3 3 MOSMOD

+ L = 5E-6

+ W = 0.1

+ AD = 1.0E-006

+ AS = 1.0E-006

+ PD = 5

+ PS = 5

.MODEL MOSMOD NMOS

+ TNOM = 25

+ LEVEL = 8 *MOSFETモデルの番号

|

|

+ MOSモデルパラメータの定義

|

.MODEL FWDIODE D

+ LEVEL = 1 *PNダイオードモデルの番号

+ TNOM = 25

+ IS = 7.4249e-013

+ N = 1.1739

|

|

+PNダイオードモデルパラメータの定義

|

.ENDS

表1に示したネットリストが基本マクロモデルとなりますが、構成するアクティブ素子のデバイスモデルの選択が重要となります。つまり表1では”LEVEL = ”と記述された数字部分を決定します。これは使用する回路シミュレータによって異なるため、それぞれのマニュアルを参照する必要があります。

MOSFETモデルの選択

先に述べたように、MOSFETのモデルを選択する考え方としては、小信号のMOSFETモデルのなかでDMOSの電気特性に近づけることができるものを選択します。考えられる特性としては、

- 非対称なドレイン抵抗、ソース抵抗特性

- ゲート電圧に依存したドレイン抵抗特性

- ドレイン電流が高くなると顕著になる自己発熱特性

- ドレイン・ソース容量特性

などがあげられます [2]。

簡単のため、ここでは1.ドレイン・ソース抵抗の非対称性と、2.ドレインエピ層のバイアス依存抵抗特性のみに着目してみます。ドレイン抵抗とソース抵抗が独立に設定でき、ドレインのバイアス依存抵抗が表現できるモデルが良いであろうという予測ができます。そこで、BSIM4を選択してみます。表1の“+ LEVEL = 8 *MOSFETモデルの番号”というところで8がBSIM4と仮定します。高耐圧MOSFETに現れる3.がサポートされていないので、完全な解決にはなりませんし、簡単のため4.についてはここでは考えません。

測定とシミュレーション結果

本実験では、DMOSの市販デバイスであるBS170 [3]を使用しました。

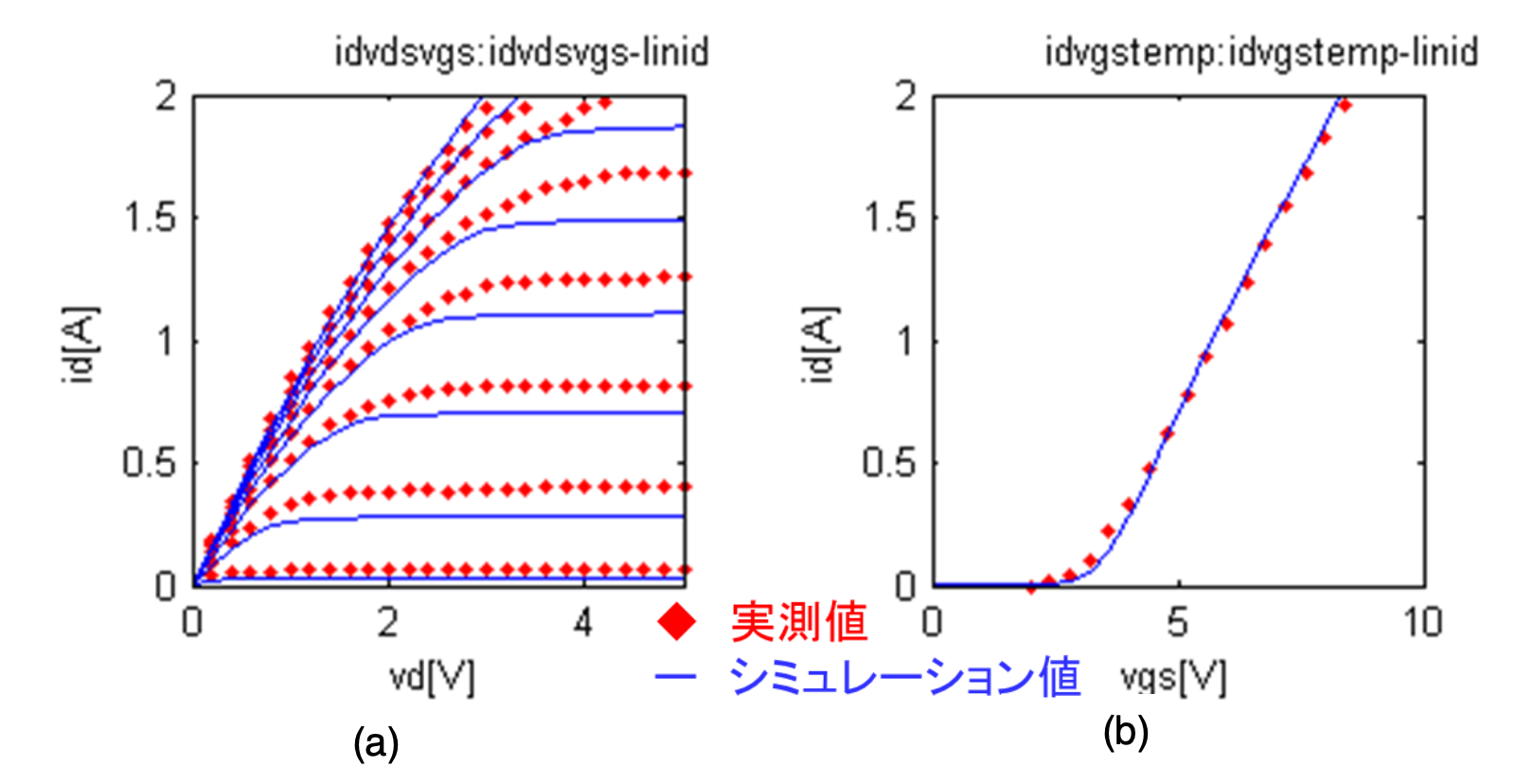

図2はBSIM4モデルによる順方向ドレイン電流特性の比較です。

(a)ドレイン電流-電圧特性 (b)ドレイン電流-ゲート電圧特性

図2 DC特性の測定値とシミュレーション値の比較

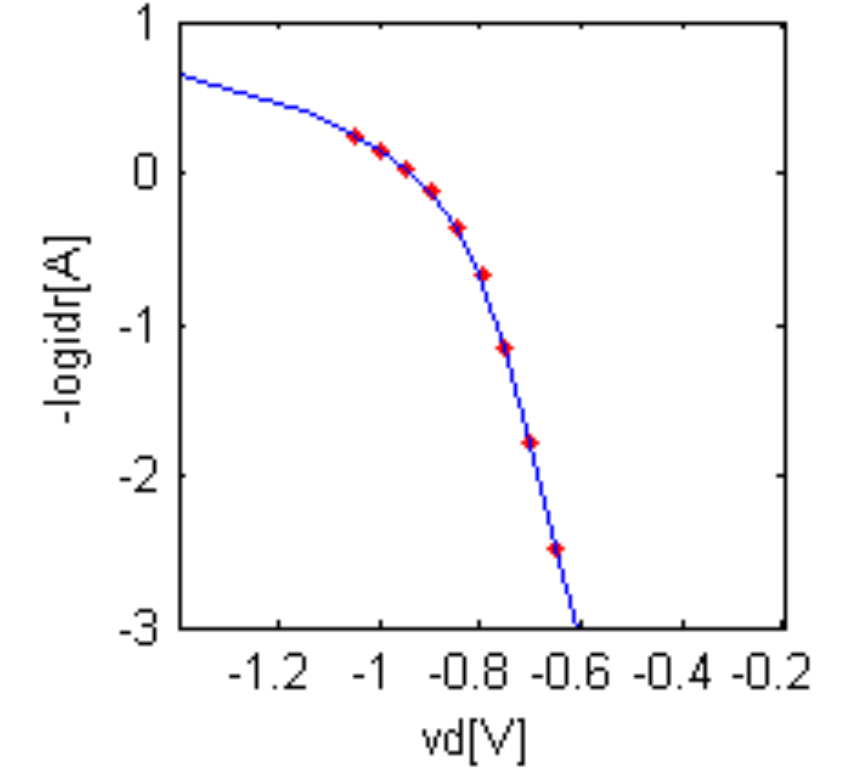

また、ソース・ドレイン間のダイオード特性については、図3のように高精度で合致しました。ここでは、電流値が大きいためPNダイオードを複数個並列に接続しています。

図3 保護ダイオード特性 (Isd-Vsd)の測定値とシミュレーション値の比較

上記のように、比較的簡単なマクロモデルを使用しましたが、BSIM4の性能によりある程度満足できる結果になりました。

マクロモデルの問題点

本マクロモデルを企業や各研究機関などで使用したいとき、個人用であればいいのですが、部署内で標準モデルとしてはデザインキットに登録しなくてはなりません。しかし、マクロモデルの登録は厄介です。また、マクロモデルに多くの能動素子エレメントが含まれる場合、比較的大きな回路のシミュレーションでは速度が遅くなります。

そこで、次回は本マクロモデルをコンパクトモデルとしてVerilog-Aで開発してみます。

参考文献

J. A. コネリー/P.チェイ 著、青木均/青木由美子 訳、「SPICEによる回路設計」、トッパン(1994)

青木均 編著, 嶌末政憲、川原康雄 著、「CMOS モデリング技術」, 丸善出版 (2006).

BS-170 MOSFET, 「BS-170データシート」、ON Semiconductor / Fairchild, 2011。

(株)モーデックでは、必要に応じてVerilog-Aによるコンパクトモデルの開発に関するご依頼をお受けいたしております。いつでもお気軽に問い合わせください。