1-1.はじめに

ご存じのように,日本では長い間最先端微細半導体デバイスの研究・開発が停滞していましたが,ついに開始の兆しが見えてきました.近い将来,再度日本が世界の最先端微細半導体研究・開発競争に参戦する日が来るのではないでしょうか.

株式会社モーデックの研究チームは,社長を含み4人のメンバーで構成されています.今まで,半導体デバイスモデリング技術の最先端を目指して,常に新しいモデルや周辺技術を研究してきました.

現在は将来のナノシートFETに対応できるモデリング技術研究を行っています.本コンテンツでは,研究状況や実験結果,成果などについて報告をアップデートしていきます.

まずは従来のPlanar型MOSFETにおけるサブ100nm化への限界を確認し,現在世界で作られている新構造FETの主な種類とその特徴についてみてみます.

次に,現在世界で研究中であり,日本が参入予定のナノシートFETについて考察します.

それらのデバイスにおいて,私たち研究チームが実施しているモデリング研究について,アップデートしていきます.

1-2.SIAゲートスケーリングロードマップ

40年以上にわたり,超大規模集積回路 (VLSI) シリコンベースの集積回路 (IC) の進化と成長は,CMOS テクノロジー,つまりトランジスタの継続的なスケーリングに行われてきました.

1960年代以来「ムーアの法則」(Moore (1965): IC デバイスの実装密度は18か月ごとに2倍になる) に忠実に従ってきました.

この構造は単にゲートに合わせて幾何学的に拡大縮小されています.短チャネル効果 (SCE) を制御するために,CMOS 製造プロセスやデバイスのドーピングプロファイルなどが複雑になりますが,最小ゲート長は30 nm です.しかし,ごく最近では,必要とされる複雑なドーピングプロファイルを確実に達成できないことや,許容可能な歩留まりで達成できないことが主な理由で,そのようなスケーリング則は停滞しています.

シリコン格子内のドーパントの避けられないランダム性により,ナノスケールMOSFETでは,デバイス特性,たとえばしきい値電圧に異常な変動が生じます.

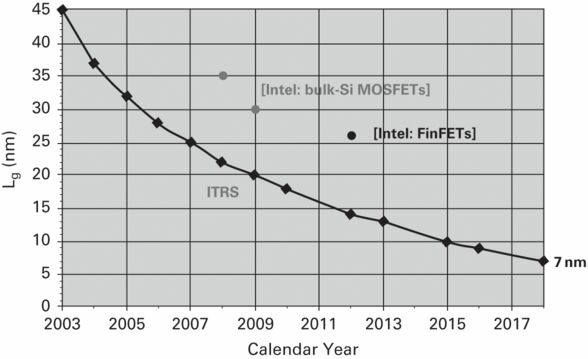

実際,このスケーリングの停滞は、半導体工業会 (SIA) の高性能集積回路 (マイクロプロセッサーや MPU など)におけるゲート長の例示的なロードマップ (SIA,1994~2011 年,2003年のITRSアップデート) 予測との比較により,図1によく反映されています.

図1.SIA ITRS が計画した高性能 CMOS ゲート長のスケーリングの例 (SIA,1994~2011年,2003 ITRSアップデート)

達成された実際のゲート長スケーリングは,IntelのMPU スケーリング結果 (Natarajan et al.,2008; Auth et al.,2012) によって示されます.明らかに,テクノロジーは予測より遅れていますが,これは一般的なケースです.

最新の予測では,2018年に ゲート長Lg = 12.8 nm,2026年にLg = 5.9 nmになるとされていますが,最新の報告によると,インテルの22 nmノードFin-FETテクノロジーでは最小Lg = 26 nmになっています.

1-3.Planar型(バルク)MOSFETのスケーリング限界 [1]

ここでは,バルクMOSFETとも呼ばれるPlanar型MOSFET構造のスケーリングが,もはや限界である理由を簡単に振り返ってみます.日本において,微細加工MOSFETが積極的に研究・開発されていた時期は,20世紀末ごろまでであったとして記述します.

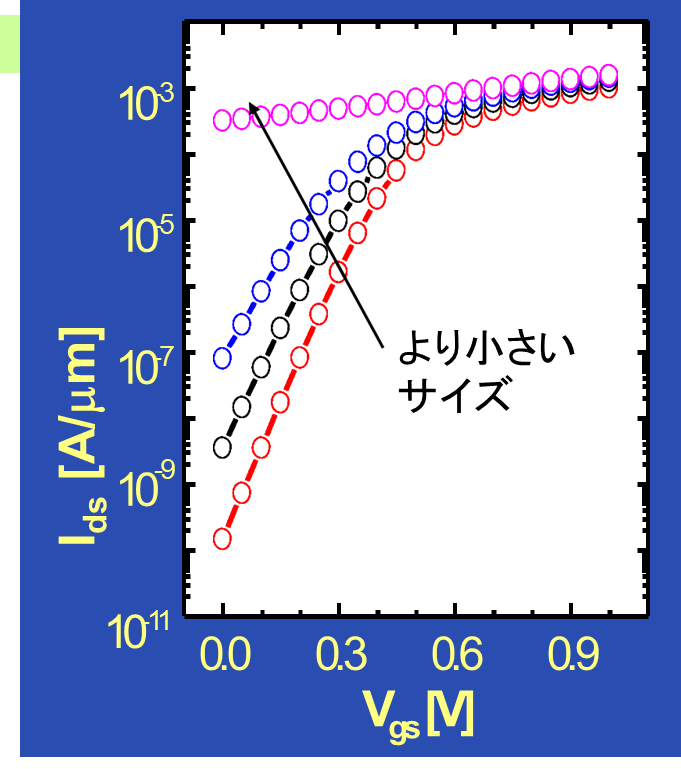

ゲート長が縮小すると,図2に示すように,MOSFETのId-Vg特性は2つの主な方法で劣化します.

図2.ゲート長縮小によるサブスレッショルドカーブの変化

まず,サブスレッショルドスイング(S)が低下し,しきい値電圧(Vt)が低下します.Vgを下げてもデバイスを簡単にオフにすることはできません.次に,SとVtはLgの変動に対してますます敏感になります.つまり,デバイスの変動がより問題になることです.これらの問題は短チャネル効果として知られています.

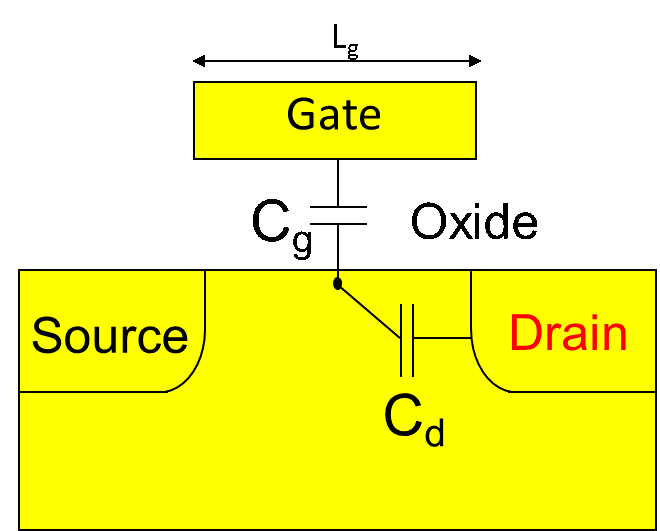

図3は,20世紀のMOSFETにおける短チャネル効果の根本原因を示しています.

Lgが減少するとCdが大きくなり,チャネル電位(チャネル障壁)をVgだけではなくVdが制御してしまう.20世紀においては,ゲート酸化膜の厚さ制御により解決していた

Vgが低下したり上昇したりすると,ゲート間容量Cgを介したチャネルの電位 (チャネルとソース間の電位障壁)変化により,トランジスタがオンまたはオフになります.理想的なトランジスタでは,チャネル電位は VgとCg によってのみ制御されます.実際のトランジスタでは,チャネル電位もCdを介してVdの影響を受けます.Lg が大きい場合,CdはCgよりもはるかに小さく,ドレイン電圧は唯一の制御電圧としてのVgの役割を妨げません.Lgが減少すると,Cdが増加し,Vgは絶対的な制御を失います.極端な場合には,図2の上部の曲線に示すように,VgはVdよりも制御性が低く,Vgを使用せずにVdのみによってトランジスタがオンになる可能性があります.その極値に達する前に,図2の他の悪化曲線が得られます.20世紀にうまく機能した解決策は,Lgに比例してゲート酸化膜の厚さを減らすことによってCgを増やすことでした.しかし,たとえ理想的な「厚さゼロ」の誘電体が利用可能だったとしても,Lgスケーリングを制限する新たな根本原因が存在します.

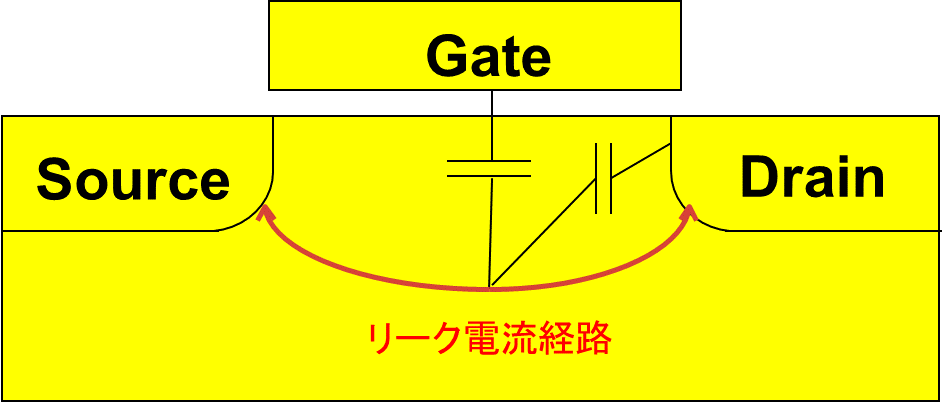

図4は,漏れ経路が界面から遠いので,漏れ電流がシリコンと誘電体の界面に沿って流れることがないことを示しています.

図4.Lgが20 nm未満では,たとえ厚さ0 nmのゲート誘電体であっても,界面から数ナノメートル下のリーク経路に沿ったVdのポテンシャル障壁の低下を阻止できない.

図4に示すゲート電極は,Vgによって弱くしか制御されないため,表面リークパスよりも低くなります.酸化膜厚がゼロでもCgは小さいからです.その結果,これらの弱く制御された経路に沿ったポテンシャル障壁は,小型Lgデバイスの大きなCdを介して,Vdによって簡単に下げることができてしまいます.これでは抵抗のように動作してしまい,もはやFETのスイッチ動作ができません.

1-4.新構造FETの開発 [1]

Planar MOSFETのスケーリング限界により,現在新しい構造のFETが研究・開発され,使用されています.様々なアプローチが行われていますが,大きく分けると,共通マルチゲート構造(CMG)と,独立マルチゲート構造(IMG)になるかと思います.

独立マルチゲート構造(IMG)

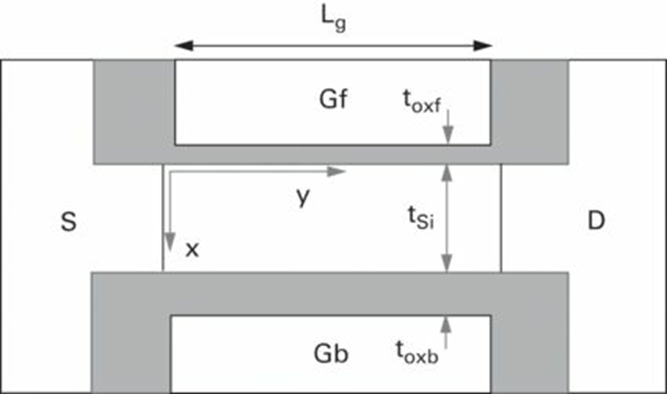

IMGによるFETには多くの種類がありますが,図5に示したのは,シンプルで代表的なデバイス構造で,ダブルゲートMOSFETと呼ばれるFETです.

図5.幅広のソース/ドレインおよびゲート-ソース/ドレインのアンダーラップを備えた一般的な DG MOSFET 構造 [2]

独立マルチゲート構造のFETでは,超薄型ボディ(UTB)にする必要があります.ボディが大変薄い(tSiが数ナノメータ―)場合,ソースとドレイン間の潜在的なリークパスは劇的に減少できます.

超薄型ボディでは,短チャネル効果を抑制するための高濃度のチャネルドーピングが不要になります.

チャネルドーピングは,短期的にはしきい値電圧を調整するために依然として使用される可能性がありますが,ゲート金属の仕事関数の調整によって,将来的になくせる可能性があります.これにより,ランダムなドーパントの変動、主かつ根本的な原因となるデバイス特性のばらつきをなくすことができます.さらに,チャネルキャリア移動度と接合リークが改善されます.ボディがドープされていない場合には,半導体と酸化物の界面の垂直な電界を低減します.また,温度,バイアスの不安定性 (負のバイアス) が改善されるはずです.

独立マルチゲートは、超薄型ボディやBOX SOIトランジスタなどの,独立したダブルゲート構造のFETです.異なるフロントゲートバイアスとバックゲートバイアス,仕事関数,誘電体の厚さ,誘電率を持ちます.図5でフォワードゲートGfとバックゲートGbに,独立したバイアス電圧を加えて動作させます.

対称 DGのSOIでは,ボディの大部分の反転電荷は,表面近くの反転電荷と同等かそれよりも高いので,オン電流の大きさなど多くの条件をコントロールできます.

しかし,問題点としてチャネル長をさらに短くするためには,tSiをさらに薄くする必要があり,プロセス技術レベル,製造装置によりその薄さを追い込めますが非常に困難です.

共通マルチゲート構造(CMG)

共通マルチゲート(CMG)FETは,1つのゲートバイアスで動作するFETです.

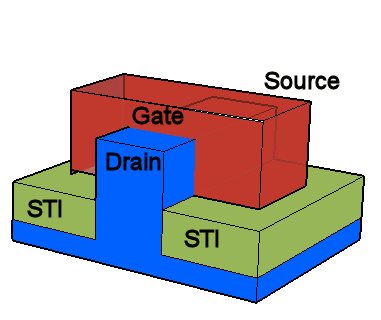

図6 の Fin-FET は,やはり薄型ボディを用いますがUTBと違って,トランジスタとして製造可能なプロセス技術で微細化を可能にします.魚のヒレのような薄いボディは,通常の露光技術とエッチング技術によって作成されます.Fin(ひれ)のように薄いボディは、シリコン・オン・インシュレータ (SOI) または低コストのバルク基板上に構築できます.また,Finはプレーナ MOSFET の加工とほぼ同じ方法でFin-FETに加工されます.これは,Finがゲート厚よりも短いため,構造が準プレーナになるためです.

図6.Fin-FETの構造概念図

Finの厚さ (ボディの厚さ) tSiがLgより小さい限り,短チャネル効果は十分に抑制され,サブスレッショルドスイング(S)は基本的に理論上の最良の状態になります.

Finの厚さをスケーリングすることでLgをスケーリングできます.たとえば,リソグラフィーとエッチングで5nmのLgを生成できる場合,tSiは約5nmで良いことになります.1999年に,18nmおよび45nmのFin-FETの動作と10nm Fin-FETのシミュレーション結果が報告されました.その後すぐに,10nm,さらに5nmのFin-FETがICメーカーから報告されました.理論的にも実際的にも,Fin-FETテクノロジーは1桁ナノメートルまで拡張可能です.

スケーリングに加えて,III-V族材料とゲルマニウムを使ったFin-FETの製造も行われています.

ゲルマニウムおよびInGaAsなどのIII-V族材料は,本質的にシリコンよりもはるかに高いキャリア移動度を持っています.これにより,デバイスのパフォーマンスが大幅に向上します.

以上のように,現在Fin-FETが微細FETで最も多く採用されています.

1-5.BSIM-CMGによるFin-FETモデリング

Fin-FETのSPICE用コンパクトモデルは,国際学会論文などで何種類か発表されていますが,業界標準として多く使用されているのは,カリフォルニア大学バークレイ校(UCB)のBSIM-CMGと思います.先に述べた独立マルチゲートFET用には,BSIM-IMGも用意されています.

BSIM-CMG は、Wire形状でも,円筒形のゲート形状を持つ柱状トランジスタでもモデル化できます.このように形状の違ったFin-FETはモデルスイッチ,GEOMODを適切に選択することでモデル化できます.

Fin-FETが形成される基板にもいくつかの種類がありますが,バルク基板またはSOI 基板の場合があると思います.BSIM-CMG は,基板選択スイッチBULKMODを選択することで,これら両方の基板上のFin-FETをモデル化することができます.

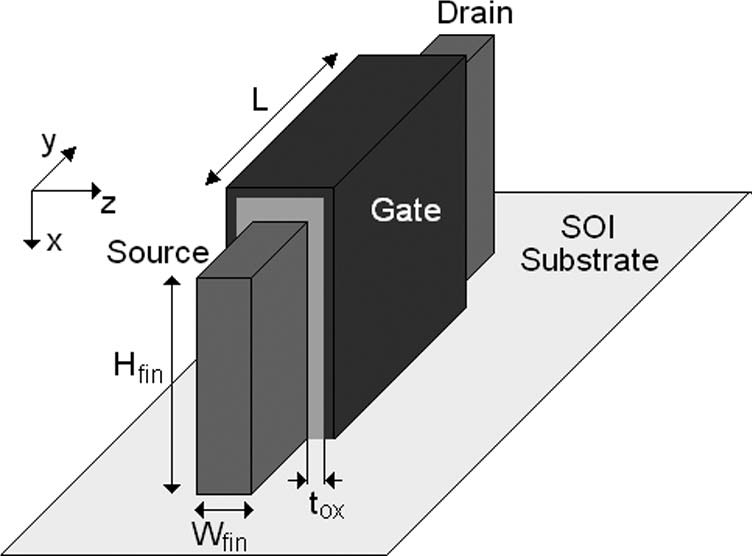

図7.対象とするFin-FETの簡易構造

Fin-FET の概略図を図7に示します [3].ここで,Wfin はフィンの幅,Hfin はフィンの高さ,Lはチャネル長です.ゲート電極はシリコンボディを3面で取り囲んでいます.3つの側面のゲート酸化膜厚はtoxです.シリコンのボディはアクセプタ濃度Naで低濃度にドープされており,ゲート材料はしきい値電圧を調整する適切な仕事関数を持つ金属です.

それぞれのインスタンス値は,Wfin = 5nm, Hfin = 30nm, L = 30nm, tox = 1nmで作成されました.

BSIM-CMGを使用した回路シミュレーションを実行するためには,Verilog-Aモデルを扱えるシミュレータが必要です.本実験では,Verilog-Aモデルをコンパイルし,無償で使用できるNGSPICEに取り込んで使用しました.モデリングは,株式会社モーデックのX-tractorまたは,X-verifierにより効率的に行えます.

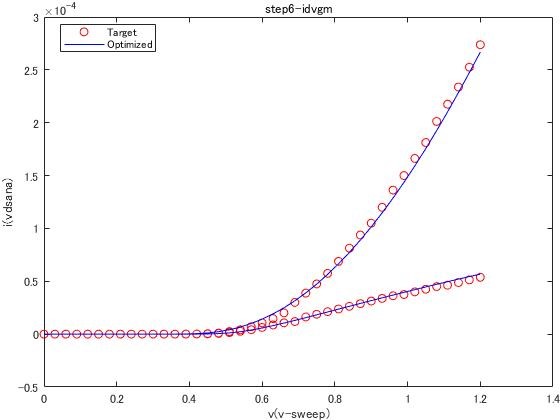

今回は,モデルパラメータをX-verifierのAIオプティマイザー機能を使用して抽出・最適化しました.AIオプティマイザーを用いることで,測定データのサブスレッショルド,線形,飽和のすべての領域について,モデルパラメータの最適な値を自動的に求めることが可能となります.

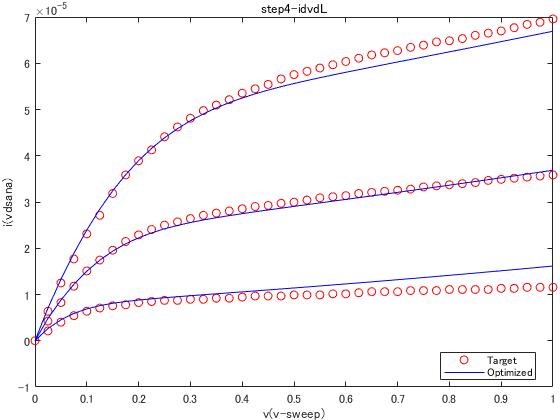

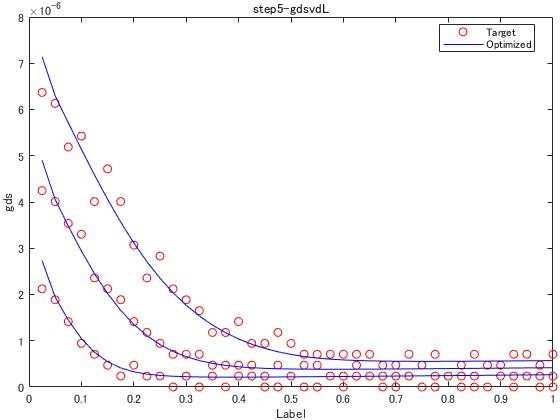

図8から図10は,測定データと抽出したモデルパラメータによる,BSIM-CMGのシミュレーションの比較プロットです.測定データとシミュレーションの誤差は,すべてにおいて4%以内になっています.

今後は静特性のみならず,高周波特性や,容量特性,ノイズ特性なども評価していく予定です.

図8.ドレイン電流対ゲート電圧特性の測定(図中ではTarget)とシミュレーション(図中ではOptimized)比較

図9.ドレイン電流対電圧特性の測定(図中ではTarget)とシミュレーション(図中ではOptimized)比較

図10.出力コンダクタンス対ドレイン電圧特性の測定(図中ではTarget)とシミュレーション(図中ではOptimized)比較

1―6.将来の超微細デバイスの研究開発

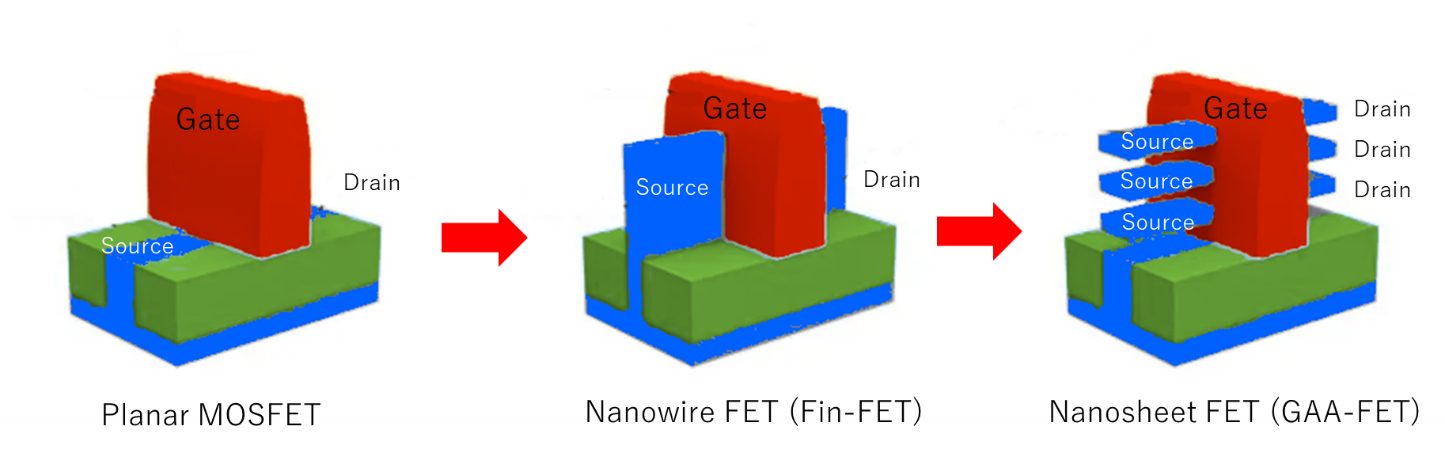

Fin-FETはNanowire FET,つまりナノレベルの線FETの一つです.チャネルが形成されるボディ部分は,最高3方向からゲートに接触しています.

図11.微細加工FET構造の流れ

Fin-FETは1つのゲートがチャネルの3方向から囲む形になるため,ゲートからのバイアス制御が効果的に行われます.さらに最も重要なことは,スケーリングによる副作用をなくせることです.また,3次元的な縦構造によって使用面積を小さくでき,回路の集積度を上げることができます.

しかし,さらなるスケーリングを行うためには,もっと効果的なゲート制御が必要です.Fin-FETの次のステップとしては,チャネルのすべての側面をゲートで囲むことです.それを行うデバイスとして候補になっているのが,Gate-All-Around FET(GAA-FET)です.「ゲートでチャネルの全体を囲むFET」という名前です.また,GAA-FETはNanosheet FET,つまりナノレベルのシートFETの一つです.

幸いなことに,BSIM-CMGはGAA-FETについても対応を宣言しており,UCBでは現在も継続開発中です.

株式会社モーデックの研究チームでは,T-CADによるシミュレーションデータや,試験的な実デバイスの測定データを入手出来次第,実験および必要であれば,モデルの改造を行う予定です.

参考文献

- [1] Y. Chauhan, D. Lu, S. Vanugopalan, S. Khandelwal, J. Duarte, N. Paydavosi, A. Niknejad, C. Hu, FinFET Modeling for IC Simulation and Design Using the BSIM-CMG Standard, ELSEVIER Inc., 2015.

- [2] J. Fossum, V. Triveri, Fundamentals of Ultra-Thin-Body MOSFETs and FinFETs, Cambridge University Press, 2013.

- [3] N. Fasarakis, A. Tsormpatzoglou, D. Tassis, I. Pappas, K. Papathanasiou, M. Bucher, G. Ghibaudo, C. Dimitriadis, “Compact Model of Drain Current in Short-Channel Triple-Gate FinFETs,” IEEE Trans. On Electron Devices, vol. 59, No. 7, 2012.

著者紹介

モーデック 最高顧問 博士(工学) 青木均 (➤ボタンをクリックすると詳細な経歴が表示されます)

【経歴】

| 1983年 | 横河・ヒューレット・パッカード入社 HP-IBシステム部 開発システム技術者 |

| 1984年 | 同社 厚木支店 フィールド技術者 |

| 1987年 | 同社 半導体システムセンタ アプリケーション開発・マーケティング技術者 |

| 1991年 | 米国Hewlett-Packard Co.招聘入社 サンタクララ事業所 モデリングソフトウエア研究開発者 |

| 1992年 | 同社モデリングチーム プロジェクトマネージャー |

| 1994年 | 米国 HP Laboratories入社 ULSI Research Lab.デバイス解析上級研究員 |

| 1995年 | Stanford大学大学院 学外講師 兼任 |

| 1996年 | University of California, Berkeley,MIT博士過程大学院 メンター 兼任 |

| 1997年 | 日本ヒューレット・パッカード(現キーサイト・テクノロジー合同会社)招聘入社デザインテクノロジーグループ長兼チーフ・デザインコンサルタント |

| 2002年 | 博士(工学) (東京工業大学 工第 2997号) |

| 2002年 | 株式会社モーデック設立 代表取締役社長就任 |

| 2002年 | 東京工業大学大学院非常勤講師 兼任 |

| 2003年 | 東京工業大学 フロンティア創造共同研究センター 特別研究員 兼任 |

| 2007年 | 大阪大学大学院 グローバルCOEプログラム非常勤講師 兼任 |

| 2009年 | 株式会社モーデック 会長就任 |

| 2010年 | 東京工業大学大学院 理工学研究科電子物理工学専攻 松澤・岡田研究室 共同研究員 兼任 |

| 2011年 | 株式会社モーデック 最高顧問就任(至現在) |

| 2011年 | 中国 清華大学マイクロエレクトロニクス研究所 共同研究員 兼任 |

| 2013年 | 群馬大学研究・産学連携戦略推進機構 産学連携・知的財産戦略室 客員教授 兼任 |

| 2014年 | 群馬大学 理工学研究院 電子情報部門 客員教授 兼任 |

| 2017年 | 帝京平成大学 大学院 環境情報学研究科/現代ライフ学部・経営学科・経営情報コース 教授 |

| 2021年 | ローム株式会社 技術顧問就任(至現在) |

【業績】

著書:2冊

訳書:1冊

国際学会・論文誌掲載:130件以上

学会活動:

IEEE Senior Member

IEEE 国際学会議長,論文誌編集委員など多数