本記事では、SPICE (Simulation Program with Integrated Circuit Emphasis)に代表される回路シミュレータで使用される、アクティブデバイス(ダイオードやトランジスタなど)のモデル作成に関する、主に学術的な情報をお伝えします。ここでは特に、ミックスド・シグナル設計検証用として注目されている言語Verilog-AMSの一部、アナログ記述用言語Verilog-Aを用いたモデル開発についてお話します。

今回は第1回として、

- なぜモデルをユーザー側が作るのか?

- どうしてVerilog-Aを使うのか?

について、簡単な例を用いて解説します。

モデル開発の必要性

アクティブデバイスを用いた電子回路設計(EDA)をコンピュータ上で行うとき、回路シミュレーションの速度、精度を向上させることは回路設計者にとって重要です。EDAユーザーである回路設計者は、常にアクティブデバイスやコンポーネント、伝送ラインなど(回路エレメント)を組み合わせてシミュレーションを行っています。これをアクティブデバイスの実動作電気特性に近くなるように、既存の回路エレメントを組み合わせて作成したものをマクロモデルと呼びます。

マクロモデルであればEDAユーザーが自由に作成できますが、手間がかかり回路設計の合間に実施するのは困難です。また、組織内で統一したデザインキットを使用して設計を行っている場合、統合されたモデルでなくては実用的ではありません。

性能の面からの欠点として、マクロモデルに使用されている回路エレメントとしてのアクティブデバイスの数が多くなるに従って、シミュレーション速度の低下が顕著になります。また、構成された等価回路に物理的な意味が少なくなり、用途が限定されてしまいます [1]。

そこで、最適なデバイスモデル開発手段について考察します。

モデル開発手段

回路シミュレータSPICEで使用するアクティブデバイスのモデルには、大きく分けて4つの作成方法が考えられます。

| モデルの種類 | 内容 | 短所 |

| CADモデル | 数学的な多項式で動作を近似したモデル | デバイスの物理的に意味の無い式なので用途が限られる |

| マクロモデル | SPICEの部品を組み合わせて動作を近似したモデル | モデルを大量に使用して回路を設計した場合,計算時間がかかる,変数を大量に使う為,収束への速度がかなり遅くなる |

| 表参照モデル | デバイスの測定を細かくし,そのデータをプロットするモデル | 測定したデバイスでしかシミュレーションできない |

| コンパクトモデル | シミュレータのソースコードレベルで等価回路,物理式,経験式を全て再現したモデル | 扱うソースコードによって,使用するシミュレータによっては使用できない |

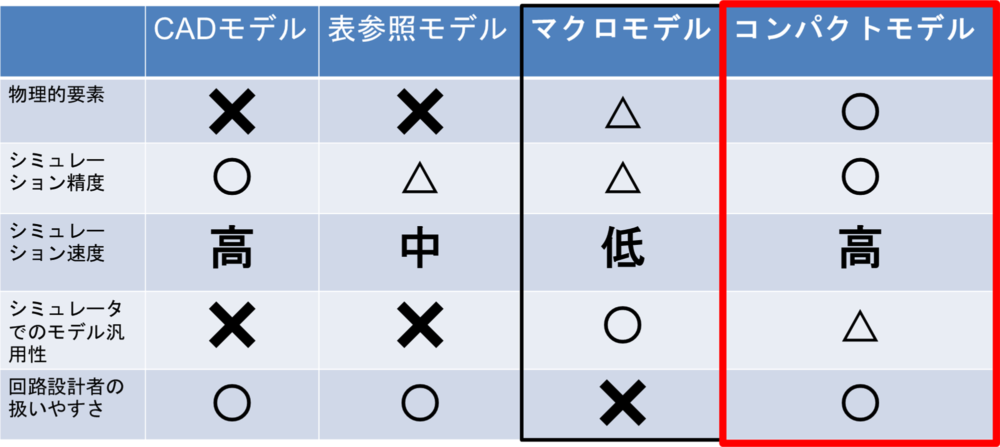

これら4つの手法において短所について何とか克服できるものが候補になりコンパクトモデルがよさそうです。さらに一般的に言われているモデルの重要ポイントを5つ挙げて比較してみます。

表2 アクティブデバイスモデルの性能比較

表2から、赤枠で囲んだコンパクトモデルに着目します。しかし、これを使用するには、シミュレータのソースコードを改造する必要があるので、表1で挙げた欠点に帰着します。

多くの市販されているSPICE系回路シミュレータでは、先に挙げたVerilog-Aによるモデル作成、使用が可能になっています。Verilog-Aによりアクティブデバイスモデルを作成すれば、モデル式だけでなく、等価回路の記述も可能となり、しかもシミュレータのユーザー側で開発できます。

ただ残念なことに、難易度は非常に高いと言えます。デバイス物理、様々な領域の電子計測、回路解析技術に加えて、プログラミングスキル(C言語を扱えるレベル)が必要です。もちろんVerilog-Aの言語を理解する必要があります。

まとめ

今回はモデル開発の必要性とその手段について考えてみました。次回からは実際にVerilog-Aを使用して、既存モデルに簡単な改造を加えてシミュレーションを行い、測定データと比較してみます。

参考文献

[1] 青木均 編著、嶌末政憲、川原康雄 著、「CMOS モデリング技術」丸善出版 (2006)。

(株)モーデックでは,必要に応じてVerilog-Aによるコンパクトモデルの開発に関するご依頼をお受けいたしております。いつでもお問い合わせください。