![]()

今回は、PDK (Process Design Kit)に含まれる『SPICEモデル』が作られるまでのお話をご紹介します。

通常、半導体設計を開始する前に、設計仕様や実績、提供されているIPの入手性などから、設計でつかうファウンドリとプロセスノード(28nm/40nmなど)を決定します。そして、いざ設計を開始する際には、ファウンドリからPDKとして、

- トランジスタや受動素子のSPICEモデル

- 各素子のライブラリ(シンボル、PCell、スタンダードセル、など)

- 検証用デザイン・ルール(DRC, LVS, ERC, Antenna)

- 各種ドキュメント

など設計に必要な材料が提供され、それを用いて回路設計を行っていきます。

回路設計者は、ここで提供されるSPICEモデルを絶対的な指標(神様)として設計を行い、製造にいたります。

SPICEモデルはこのように非常に重要な位置づけにありますが、トランジスタのモデリングを行うのはファウンドリ側の作業なので、どうやってモデルが作られるのか?というのを知る機会が少ないかと思います。

以上の背景より、今回は、あまり設計者が関わることのない、PDKに含まれるSPICEモデルがどのようにして作られるのかをご紹介していきたいと思います。

※ ここで「トランジスタ」と表現しているものは、すべてMOSFETを想定しています。

PDKに含まれるトランジスタ・モデルの作製プロセスを一挙解説!!

PDKのSPICEモデルを作るまで、以下の5つのステップを経て、設計者のもとに届けられます。

TEG (Test Element Group)の設計

⇓

TEG製造

⇓

TEG測定

⇓

パラメータ抽出(モデリング)

⇓

PDKパッケージとして提供

ステップ1:TEG (Test Element Group)の設計

デバイス素子の特性が安定してきたら、実際にテスト用のウエハを作製します。これをTEG(テグ)と呼びます。

TEGもやみくもに作ればよい訳ではなく、戦略的に様々なバリエーションを埋め込んでいきます。

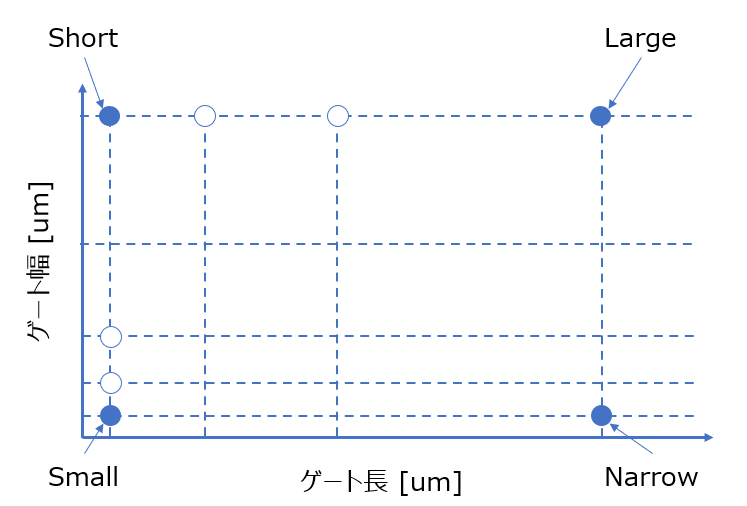

上図のLargeと示されているケースは、短チャネル長効果や狭チャネル幅効果が生じないように十分ゲート長が長く、ゲート幅が広いデバイスを示しています。

Shortはプロセスの最小ゲート長を有するデバイスで、ゲート幅はLargeと同じスケールのケースです。そして、Narrowはプロセスの最小ゲート幅を有するデバイスで、ゲート長はLargeと同じスケールにしたケースです。最後に、Smallはプロセスの最小ゲート長と最小ゲート幅を有するデバイスを示しています。

これら4つのコーナーデバイスは、デバイス形状に依存する関係性を表現するために最低限必要なバリエーションになります。

特にLargeデバイスは、トランジスタのしきい値電圧や移動度関係の基礎パラメータを抽出するために必要となります。

また、LargeからShortにかけてゲート長が短くなるデバイスは、トランジスタの短チャネル長効果パラメータを抽出するために使用されます。そして、LargeからNarrowは狭チャネル幅効果、ShortからSmallは縮小効果を表現するモデルパラメータの抽出に必要となってきます。

ステップ2:TEG製造

次に、TEGを実際に製造していきます。

ステップ3:TEG測定

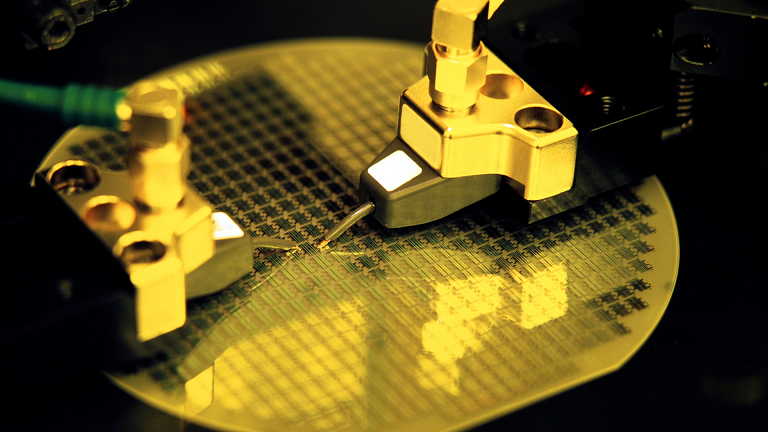

TEGがウエハとしてあがってくると、今度はそれを実際に測定していきます。

ウエハのままプローブを当てて測定ができる特殊な計測装置を用いて、ステップ1で設計したさまざまなバリエーションのデバイスに対して、一つひとつトランジスタ特性を計測していきます。TEGではトランジスタ単体を測定できるように、トランジスタの4端子(ゲート、ドレイン、ソース、バルク)専用のパッドが引き出されています。

顕微鏡を覗きながら、そのパッドに対して、プローブを慎重に落として、実際に測定をしていきます。特に周波数の高い測定では、雰囲気温度や電源環境だけでなく、このプローブの当たり方だけでも測定結果が変わってしまうため、この測定技術は極めて特殊な技術が必要となってきます。

また、プローブそのものも寄生素子として測定結果に乗ってきてしまうため、それを取り除くDe-embedded(ディ・エンベデッド)という作業も極めて重要になってきます。

ステップ4:パラメータ抽出(モデリング)

こういった高度な測定を経て取得したさまざまなトランジスタの特性をもとに、今度はそのデータを参照して、パソコン上でも同じ特性を得られる擬似的なデバイスを作っていきます。

これがまさにPDKに提供される『SPICEモデル』の原型になります。

MOSFETであれば、BSIM(ビーシム、Berkeley Short-channel IGFET Model)と呼ばれるモデルがデファクト・スタンダードとして用いられています。

いわゆるトランジスタ・モデルのテンプレートみたいなもので、数百にもおよぶパラメータが事前に与えられており、その裏側にはトランジスタの電気的特性や物理的な特性などを表現した数式が埋め込まれています。基本的には、モデリング・エンジニアは、この係数(パラメータ)を実際の測定データとマッチするように、モデリング専用のツールを使って合わせ込みを行っていきます。

これを「パラメータ抽出」と呼んでいます。

BSIMモデル単体でも数百のパラメータを持ち、それをすべて電気的・物理的背景を理解しながら合わせ込むだけでも至難な技なのですが、BSIMモデルはあくまで汎用的なテンプレートのため、本当のデバイス特性を表現するには、独自にモデルをカスタマイズしなくてはいけません。

これがまさに『モデリング技術』の難しいところであり、また、そういった希少性の高い極めて重要な技術力を長年蓄積してきた弊社・モーデックのバリューでもあります。弊社が提供しているモデリング・サービスの種類に関しては、こちらをご覧ください。

ステップ5:PDKパッケージとして提供

以上のプロセスを経て、ようやくトランジスタ・モデルとして形になったものが、PDKパッケージとして半導体設計者の元へ届けられます。

まとめ

今回は、PDKに含まれるトランジスタ・モデルはどのようにして作られるか?というテーマでお話してきました。

こうやって見てみると、設計者の手元に届くまでに、とても複雑で難解なモデリングプロセスを経てきていることがお分かりいただけるかと思います。昨今はファウンドリも海外主流へ移ってきており、なかなかこのトランジスタのモデリングの裏側を垣間見える機会も少なくなってきているかもしれません。