## 「PDK用高精度デバイスモデリングサービス」

本高精度デバイスモデリングサービスは、半導体のチップもしくはウェハ上に搭載されたアクティブデバイスとパッシブデバイスを対象(プロセスはレガシーから最先端プロセスまで)としています。出来上がったモデルは、PDK(Process Design Kit)内のモデルとして使用することができます。モデリング対象となる測定データは、通常 FAB が保証している範囲以外の極低温下の測定データも含みます。以下に、対応デバイス、モデル、シミュレータ例を示します。

| Si系デバイス  | ■ CMOS/SOI-CMOS/SOS-CMOS ■ HVMOS ■ LDMOS/DMOS ■ IGBT ■ BJT ■ ダイオード                                                                      |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 化合物系デバイス | ■ SIC MOSFET ■ GaN-HEMT ■ HEMT ■ MESFET ■ HBT ■ 各種ダイオード                                                                                 |

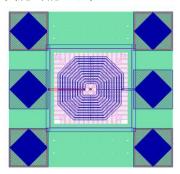

| その他デバイス  | ■ ポリ抵抗 ■ キャパシタ(MOS/MIM/MOM) ■ スパイラルインダクタ<br>■ 伝送線路/スタブ/結合線路                                                                             |

| モデル      | ■ BSIM3 ■ BSIM4 ■ BSIM6 ■ BSIM-SOI4 ■ HiSIM2 ■ HiSIM-HV ■ Gummel-Poon ■ VBIC ■ MEXTRAM504 ■ HiCUM ■ Diode ■ EEHEMT ■ Angelov ■ 各種マクロモデル |

| シミュレータ   | ■ HSPICE® ■ Spectre® ■ Eldo® ■ ADS ■ PSpice® ■ LTspice ■ ngspice ■ UCBSpice3f5                                                          |

https://www.modech.com/service\_and\_products/pdk\_spice\_modeling/より引用

## モーデック社が実施する高精度 CMOS モデリングの特徴について解説します。

・FAB が提供している PDK 内のコンパクトモデル (例えば BSIM3/4/Bulk, BSIM-CMG, HiSIM-HV など) との動作整合性を維持しながら、モンテカルロ解析やミスマッチ解析を想定した CMOS 高精度デバイスモデリングを実施可能です。

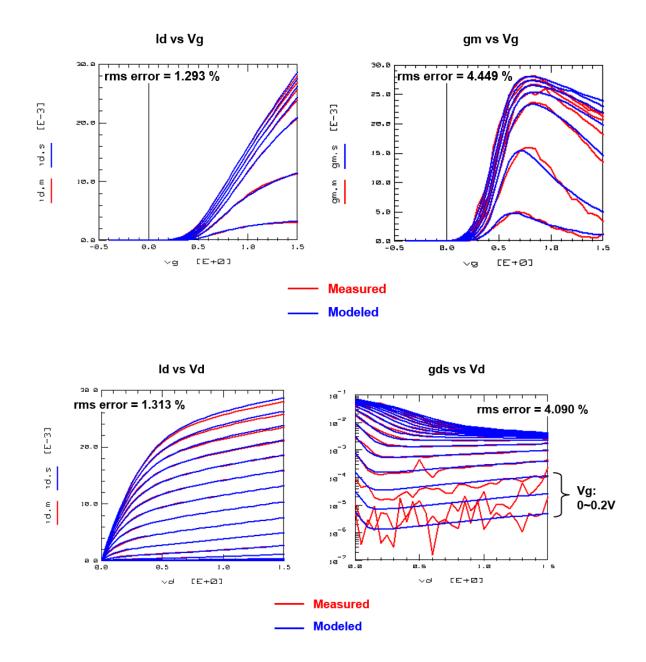

・通常、目標の DC モデリング精度(Id-Vg, Id-Vd など)は、rms(root mean square)誤差で $\pm 5\%$ 以内とします。また、微分特性(gm, gout など)に対する目標モデリング精度は、rms 誤差で $\pm 10\%$ 以内とします。

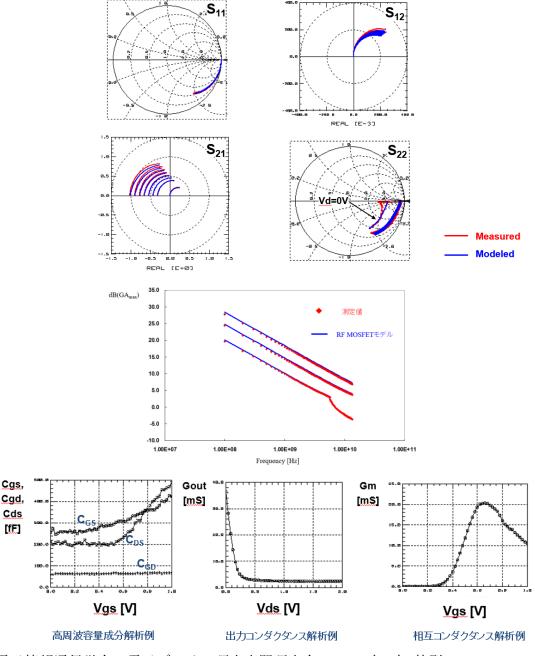

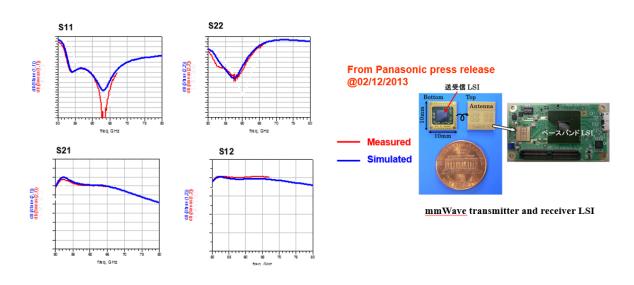

・S パラメータモデリングに関しては、目標精度を複素数の振幅と位相に対して rms 誤差で±10%以内 (DC の微分特性と同等) とします。S11 と S22 のスミスチャート、S12 と S21 の極座標、MSG (Maximum Stable Gain) / MAG (Maximum Available Gain)、H21、K ファクタ、

群遅延、高周波 gm, cgs、cgd、cds の周波数分散特性などを用いて、理論的に妥当性のある結果であることを説明します。高周波 gm, cgs、cgd、cds のバイアス依存特性に対しては合理的な周波数を選定し、その技術的な理由を説明します。S パラメータから変換する算出式を示します。

電子情報通信学会 電子デバイス研究専門研究会 2017 年 春 特別ワークショップ「RF-CMOS の S パラメータ測定によるモデリング手法」より引用

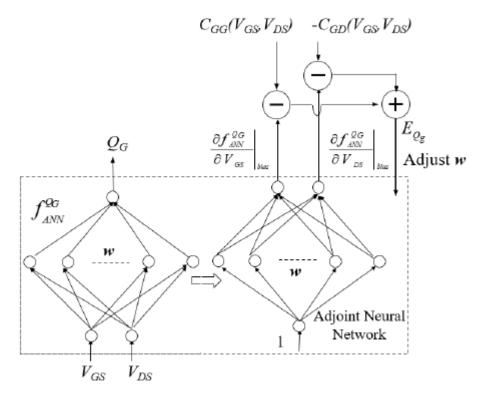

・IEEE 論文である"Artificial Neural Network Modelling for Cryo-CMOS Devices"を参考にした MOSFET ニューラルネットワークモデルを提供可能です。MOSFET ニューラルネットワークモデルは、そのアルゴリズム的に微小電流領域のノイズに弱いため、その対応を施すように留意します。必要に応じて、その対処法を説明します。

"Artificial Neural Network Modelling for Cryo-CMOS Devices"より引用

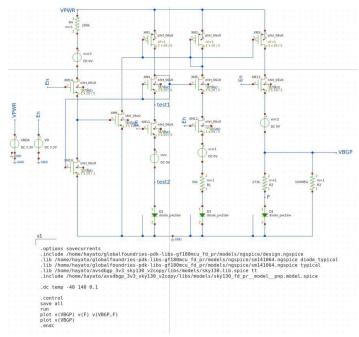

・CMOS デバイスのコンパクトモデル式を改変する場合は、アナログハードウェア記述言語 Verilog-A を使用します。必要に応じて、その改変内容の妥当性を説明します。

```

begin

t0 = vgd + `DELTA_1;

t1 = sqrt(t0 * t0 + 4.0 * `DELTA_1);

t2 = 0.5 * (t0 - t1);

t3 = weffcv * cgdl;

t4 = sqrt(1.0 - 4.0 * t2 / ckappad);

cgdo = param_cgdo + t3 - t3 * (1.0 - 1.0 / t4) * (0.5 - 0.5 * t0 / t1);

qgdo = (param_cgdo + t3) * vgd - t3 * (t2 + 0.5 * ckappad * (t4 - 1.0));

t0 = vgs + `DELTA 1;

```

```

t1 = sqrt(t0 * t0 + 4.0 * `DELTA_1);

t2 = 0.5 * (t0 - t1);

t3 = weffcv * cgsl;

t4 = sqrt(1.0 - 4.0 * t2 / ckappas);

cgso = param_cgso + t3 - t3 * (1.0 - 1.0 / t4) * (0.5 - 0.5 * t0 / t1);

qgso = (param_cgso + t3) * vgs - t3 * (t2 + 0.5 * ckappas * (t4 - 1.0));

end

```

Verilog-A モデル式例

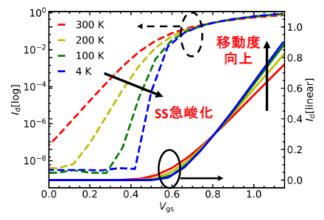

・極低温においては、Id-Vg シミュレーション結果から得られるしきい値とその近傍の傾きに関して極低温効果を確認し、技術的に妥当性のある結果であることを説明します。必要に応じて、極低温モデリングで新たに判明した技術要点を示します。

電子情報通信学会総合大会 2025「Cryo-VLSI 設計環境のためのトランジスタモデル開発」より引用

- ・回路検証を実施する場合、CMOS 高精度モデルでインバータ回路やリングオシレータ回路の ミュレーションなどを行い、モデル動作に問題ないことを確認します。

- ・CMOS 高精度モデリング結果レポートには、測定とシミュレーションの比較結果や回路検証 結果(回路検証まで実施した場合)を掲載します。

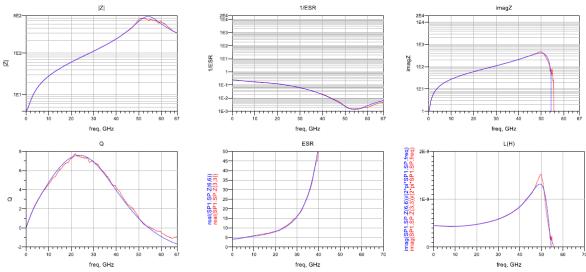

## モーデック社が実施する高精度パッシブデバイスモデリングの特徴について解説します。

・FAB が提供している PDK 内のパッシブデバイスモデル(例えば抵抗、キャパシタ、スパイラルインダクタなど)との動作整合性を維持しながら、モンテカルロ解析を想定した高精度パッシブデバイスモデリングを実施可能です。

- ・IEEE 論文である"Artificial Neural Network Modelling for Cryo-CMOS Devices"を参考にしたパッシブデバイスニューラルネットワークモデルを提供可能です。パッシブデバイスニューラルネットワークモデルは、そのアルゴリズム的に微小電流領域のノイズに弱いため、その対応を施すように留意します。必要に応じて、その対処法を説明します。

- ・高精度パッシブデバイスモデリング結果レポートには、測定とシミュレーションの比較結果 を掲載します。極低温下等のような特別な条件においては、新たに判明した技術要点を示しま す。

## モーデック社が実施するユーザー回路に対する検証内容の特徴について解説します。

・ユーザー側の回路検証において、収束性(発散)の問題が発生した際には、回路設計者と協力し、モデル起因、回路起因、シミュレータ要因を切り分け、その技術レポートを提出し説明します。

・収束性問題がモデル起因であった場合、速やかにモデル修正、改善を実施し提出します。また、モデルの修正内容を明確に説明します。